Introduction

The Vollo SDK is designed for low latency streaming inference of machine learning (ML) models on FPGA platforms.

Evaluation

You can easily discover the latency Vollo can achieve for your models, without needing an FPGA or a Vollo license. Use the online Vollo Sandbox.

Alternatively, you can download and install the Vollo SDK on your own computer if you wish to evaluate Vollo offline. You won't need an FPGA or a Vollo license for this either. See Getting Started for details.

User Guide Overview

This document outlines the following:

- Installation

- Key features of Vollo

- Steps to get started with Vollo

- The Vollo Compiler API

- The Vollo Runtime API

- Hardware requirements and setup

Installation

The latest SDK is available for download from https://github.com/MyrtleSoftware/vollo-sdk/releases.

Download the vollo-sdk-<version>.run self-extractable archive and execute it

to extract the Vollo SDK contents to the current directory.

chmod +x vollo-sdk-<version>.run

./vollo-sdk-<version>.run

Key Features

Vollo accelerates machine learning inference for low latency streaming models typically found in financial trading or fraud detection systems such as:

- Market predictions

- Risk analysis

- Anomaly detection

- Portfolio optimisation

Vollo is able to process of range of models, including models which maintain state while streaming such as recurrent models and convolutional models.

Key characteristics of Vollo are:

- Low latency inference of machine learning models, typically between 2-10μs.

- High accuracy inference through use of Brain Floating Point 16 (bfloat16) numerical format.

- High density processing in a 1U server form factor suitable for co-located server deployment.

- Compiles a range of PyTorch models for use on the accelerator.

Getting Started

You can get started with evaluating your ML model's performance on Vollo using the Vollo compiler and Vollo virtual machine (VM), which don't require an FPGA accelerator.

When you are ready, you can run inferences with your model on a Vollo FPGA accelerator using an evaluation license.

Performance estimation and model design with the Vollo compiler

You can use the Vollo compiler and VM to compile and estimate the performance of your model in an ML user's environment without any accelerator.

The Vollo compiler and Vollo VM execution time is typically on the order of seconds, enabling fast model iteration for tuning models to meet a latency target.

To estimate performance of your model with the Vollo SDK:

-

Download and extract the Vollo SDK.

-

Install the Vollo compiler Python libraries.

-

Compile your model using the Vollo compiler and run the compiled model in the Vollo VM to generate a compute latency estimate that will be achieved with Vollo.

See Vollo compiler Example 1 for a fully worked example of this including performance estimation.

-

Add in IO latency for your model characteristics in order to estimate end to end latency.

-

Iterate on your model architecture to meet your combined latency and accuracy requirements.

Validating inference performance using the Vollo FPGA accelerator

When you are ready to run inferences with your models on a Vollo accelerator, you will need a compatible FPGA based PCIe accelerator card and a Vollo license.

Evaluation licenses can be provided free of charge by contacting vollo@myrtle.ai.

To validate inference performance on Vollo:

-

Follow the steps to program the Intel Agilex, AMD V80 or Silicom Artena and license the FPGA.

-

Compile your model and save it as a

.volloprogram file using the Vollo compiler.See Vollo compiler Example 1 for a fully worked example.

-

Run and benchmark your model on the accelerator using the Vollo runtime C example.

Make sure to pass the example application the path to your saved

.volloprogram when you invoke it on the command line.

Note that the Vollo SDK includes prebuilt FPGA bitstreams for selected PCIe accelerator cards so no FPGA compilation or configuration is required after initial accelerator setup. As a result loading user models to run on Vollo takes under a second, enabling fast onboard iteration and evaluation of different models.

Vollo Compiler

The Vollo compiler is made up of 2 Python libraries:

- The

vollo-torchPyTorch frontend to the compiler. - The

vollo-compilerbackend that can transform and compile a model to a Vollo program (.vollofile).

The Vollo Runtime section describes how to run a Vollo program on a Vollo accelerator. The Vollo compiler API also includes functionality to simulate and estimate performance of Vollo programs.

Installation

Set up Vollo environment variables by sourcing

setup.sh in bash

from the Vollo SDK root directory.

Install the wheel files for the Vollo compiler libraries. It's recommended that you install these into a virtual environment.

Note: the packaged wheels only support python 3.7 or greater

python3 -m venv vollo-venv

source vollo-venv/bin/activate

pip install --upgrade pip

pip install "$VOLLO_SDK"/python/*.whl

API Reference

This chapter walks through examples of how to use the Vollo compiler that should cover the most commonly used parts of the API.

The API Reference contains a more complete list of all available classes and methods.

Supported Models

The Vollo compiler supports PyTorch models that use the following operations:

| Operation | Support Notes | Fp32 Support |

|---|---|---|

| Pointwise arithmetic ops | +, -, *, /, maximum, minimum, the pointwise overload of max and min | ✅ +, -, *, maximum, minimum |

| Inequality | >, <, >=, <= | ✅ |

| Clamp ops | clamp, relu | ✅ |

| Matrix multiplication | Linear; matmul / @ where one side is a constant | ❌ |

| Convolution | Via vollo_torch.nn.PaddedConv1d, with groups == 1 or groups == in_channels == out_channels | ❌ |

| LSTM | torch.nn.LSTM, vollo_torch.nn.LSTM | ❌ |

| Indexing / slicing | Partial square bracket [] support; index_select, narrow | ✅ |

sum | keepdim = True required when summing over data dimension | ❌ |

where | If the where condition is an inequality comparison | ✅ |

| Concatenation | cat, concat, concatenate | ✅ |

| Stacking | stack, vstack, row_stack, hstack, column_stack, dstack | ✅ |

LayerNorm | ❌ | |

RMSNorm | via vollo_torch.nn.RMSNorm for torch versions < 2.4 | ❌ |

| Batch Normalization | BatchNorm1d, BatchNorm2d, BatchNorm3d | ✅ |

| Transposing | transpose, swapdims, swapaxes, t, T, mT, permute; See data dimension | ✅ |

squeeze, unsqueeze | ✅ | |

| Reshaping | reshape, view, reshape_as, view_as, flatten; Stride of data dimension must be unchanged | ✅ |

| Broadcasting | Implicitly or with broadcast_to, broadcast_tensors, expand, expand_as | ✅ |

sqrt | torch.sqrt, torch.rsqrt | ❌ |

tanh | torch.tanh, torch.nn.Tanh | ❌ |

| Exponential | torch.exp, torch.exp2 | ✅ |

silu | torch.nn.functional.silu, torch.nn.SiLU | ❌ |

softplus | torch.nn.functional.softplus, torch.nn.Softplus | ❌ |

softmax | torch.softmax, torch.nn.Softmax | ❌ |

sigmoid | torch.sigmoid, torch.nn.functional.sigmoid, torch.nn.Sigmoid | ❌ |

gelu | torch.nn.functional.gelu, torch.nn.GELU | ❌ |

Models that take multiple input tensors and return multiple output tensors (i.e. a tuple of tensors) are supported.

Note that for operations like Dropout and BatchNorm1d (which change behaviour at inference time) to be handled correctly, the model should be in eval mode.

TorchScript

The Vollo compiler supports standard PyTorch modules (torch.nn.Module); it

does not support TorchScript modules (torch.jit.ScriptModule).

Example 1: MLP

Basic models like multilayer perceptrons (MLP) can be defined without any changes from a standard PyTorch definition.

import torch

import torch.nn as nn

import torch.nn.functional as F

class MLP(nn.Module):

def __init__(self, input_size, output_size, hidden_size):

super().__init__()

self.fc1 = nn.Linear(input_size, hidden_size)

self.fc2 = nn.Linear(hidden_size, hidden_size)

self.out = nn.Linear(hidden_size, output_size)

def forward(self, x):

x = F.relu(self.fc1(x))

residual = x

x = F.relu(self.fc2(x)) + residual

return self.out(x)

# Instantiate the model

input_size = 784

output_size = 10

hidden_size = 128

model = MLP(input_size, output_size, hidden_size)

The first stage of compiling a model is to lower it to NNIR. NNIR is the Vollo compiler's intermediate representation for representing neural network graphs. NNIR sits at a similar level of abstraction to ONNX, with most NNIR operators having direct ONNX or PyTorch analogues.

import vollo_torch

# An input to the model needs to be provided so that its execution can be

# traced

input = torch.randn(input_size)

# Trace the model's execution to annotate it with activation shapes

(model, expected_output) = vollo_torch.fx.prepare_shape(model, input)

nnir = vollo_torch.fx.nnir.to_nnir(model)

NNIR can be compiled to a Vollo program given a Vollo accelerator configuration. You can find the preset configurations that can be instantiated in the API reference.

import vollo_compiler

# Replace the Config in the line below with the Config for the accelerator you

# are using

config = vollo_compiler.Config.amd_v80_c6b32()

program = nnir.to_program(config)

Vollo programs have all their memory allocated statically. You can print the static resource usage of a program like this:

print(program.metrics())

Save the program to a file so that it can be used for inference by the Vollo runtime.

program.save('mlp.vollo')

Simulation

The Vollo compiler can be used to simulate programs in the Vollo virtual machine (VM). This is an instruction level simulation of the Vollo accelerator which can be used to:

- Estimate performance of a model. The VM is not cycle accurate but provides an indicative cycle count of a model.

- Verify the correctness of the compilation stages, including the effect of quantisation.

Construct a VM instance with your program loaded. Run the VM by passing it a numpy array of the input. It should produce the same result as the source PyTorch model, within some range of floating point error.

vm = program.to_vm()

vm_output = vm.run(input.detach().numpy())

torch.testing.assert_close(expected_output, torch.from_numpy(vm_output), atol = 1e-2, rtol = 1e-2)

print("cycle count:", program.cycle_count_per_inference())

# Translate the estimated cycle count to a duration for the compute (not

# including IO) in microseconds, using the bitstream clock speed (320 MHz)

print(f"latency (compute): {program.compute_duration_per_inference_us():.1f}us")

The VM records the number of cycles the program took to execute.

Note there will be some discrepancy between the VM's cycle count and the true

cycle count, so the VM's cycle count should be treated as an estimate.

Also note that the VM does not model the latency of the communication between

the host and the Vollo accelerator. This communication latency can be estimated

using our IO Round Trip benchmarks.

Example 2: CNN

Vollo supports streaming 1D convolutional neural networks (CNNs), which might require you to make some changes to your model if you are currently using a non-streaming 1D CNN.

A streaming convolution applies the convolutional kernel to the most recent window of the input sequence as the data points in the input sequence arrive. This differs from a non-streaming convolution, which expects to receive a complete input sequence and applies its convolutional kernel to each window of that input.

Streaming convolutions will have much lower latency than non-streaming

convolutions, but they have to maintain some state, namely the most recent

window of input, making them unnatural to define in ML frameworks like PyTorch.

To enable the use of of streaming convolutions, the Vollo compiler includes a

streaming_transform which transforms a non-streaming CNN into a streaming CNN,

as long as the non-streaming CNN meets certain constraints.

Using the streaming_transform

The model below is a non-streaming CNN taking an input sequence of length 5 and producing an output of length 1. (It can actually take any input sequence of length 5+n and produce an output of length 1+n, but we will only consider the minimal sequence length, since that is the length of the input context used by each of the output elements.)

import torch

import torch.nn as nn

import torch.nn.functional as F

class CNN(nn.Module):

def __init__(self, in_channels, out_channels, hidden_channels, kernel_size=3):

super().__init__()

# Reduces sequence length by (kernel_size - 1) = 2

self.conv1 = nn.Conv1d(in_channels, hidden_channels, kernel_size)

# Reduces sequence length by (kernel_size - 1) = 2

self.conv2 = nn.Conv1d(hidden_channels, out_channels, kernel_size)

def forward(self, x):

x = F.relu(self.conv1(x))

x = F.relu(self.conv2(x))

return x

# Instantiate the model

in_channels = 32

out_channels = 1

hidden_channels = 128

model = CNN(in_channels, out_channels, hidden_channels)

In order to apply the streaming_transform, the torch.nn.Conv1d layers need

to be replaced with vollo_torch.nn.PaddedConv1d layers.

import torch

import torch.nn as nn

import torch.nn.functional as F

import vollo_torch.nn

class CNN(nn.Module):

def __init__(self, in_channels, out_channels, hidden_channels, kernel_size=3):

super().__init__()

self.conv1 = vollo_torch.nn.PaddedConv1d(in_channels, hidden_channels, kernel_size)

self.conv2 = vollo_torch.nn.PaddedConv1d(hidden_channels, out_channels, kernel_size)

def forward(self, x):

x = F.relu(self.conv1(x))

x = F.relu(self.conv2(x))

return x

# Instantiate the model

in_channels = 32

out_channels = 1

hidden_channels = 128

model = CNN(in_channels, out_channels, hidden_channels)

These PaddedConv1d layers are identical to torch.nn.Conv1d, but with left

padding pre-applied to the input so as not to reduce the sequence length.

This PaddedConv1d model is still a non-streaming model, which now takes an

input sequence of length 5 and produces an output of length 5.

Its relationship to the original Conv1d model is that, given the same model

parameters (weights, biases, etc.) and input sequence, the last element of the

output sequence of the PaddedConv1d model will be equal to the last/only

element of the output sequence of the Conv1d model.

The PaddedConv1d model can be lowered to NNIR and have the

streaming_transform applied.

batch_size = 1

sequence_length = 5

input = torch.randn(batch_size, in_channels, sequence_length)

(model, expected_output) = vollo_torch.fx.prepare_shape(model, input)

nnir = vollo_torch.fx.nnir.to_nnir(model)

# Provide the streaming transform with index of the sequence axis

(nnir, output_axis) = nnir.streaming_transform(2)

The resulting NNIR graph represents a streaming CNN, i.e. containing state, that takes a single data point of a sequence as input and produces a single data point as output, updating its input window state in the process. Input sequences for the streaming CNN need to be fed in sequentially, e.g. in a loop. For example, using the VM:

import vollo_compiler

# Replace the Config in the line below with the Config for the accelerator you

# are using

program = nnir.to_program(vollo_compiler.Config.amd_v80_c6b32())

vm = program.to_vm()

vm_outputs = []

for i in range(5):

# Runs inference on one element of the input sequence, updating the

# streaming CNN's state

vm_outputs.append(vm.run(input[:, :, i].detach().numpy()))

torch.testing.assert_close(

expected_output,

torch.stack(

[torch.from_numpy(output) for output in vm_outputs],

axis=output_axis,

),

atol = 1e-2,

rtol = 1e-2

)

The streaming CNN satisfies the property that, given an input sequence, the i-th element of the output sequence of the non-streaming CNN will be equal to the output of the i-th iteration of feeding the input to the streaming CNN.

The streaming CNN can be saved and run on the accelerator like any other program:

program.save('cnn.vollo')

Example 3: LSTM

Vollo supports both streaming and non-streaming LSTM models.

Non-streaming LSTM model

To compile an LSTM model as a non-streaming model, you can follow the steps outlined in Example 1: MLP of lowering the model to NNIR, and then compiling it with an accelerator config.

import torch

import torch.nn as nn

import vollo_compiler

import vollo_torch

class LstmNet(nn.Module):

def __init__(self, input_size, hidden_size, num_layers, output_size):

super().__init__()

self.lstm = nn.LSTM(input_size, hidden_size, num_layers=num_layers)

self.linear = nn.Linear(hidden_size, output_size)

def forward(self, x):

x, _ = self.lstm(x)

x = self.linear(x)

return x

input_size = 128

hidden_size = 256

num_layers = 2

output_size = 16

model = LstmNet(input_size, hidden_size, num_layers, output_size)

seq_length = 20

input = torch.randn(seq_length, input_size)

# Trace the model's execution to annotate it with activation shapes

(model, expected_output) = vollo_torch.fx.prepare_shape(model, input)

nnir = vollo_torch.fx.nnir.to_nnir(model)

# Replace this config with the one for the accelerator you are using

config = vollo_compiler.Config.amd_v80_c6b32()

program = nnir.to_program(config)

The example above will give a Vollo program which takes an input tensor of size 20 x 128,

and will output a tensor of size 20 x 16. This is a non-streaming LSTM model, since it takes

an entire sequence as input.

As in Example 1: MLP we can construct a VM instance to simulate the Vollo accelerator, allowing us to get bit-accurate results from the compiled model, and a latency estimate.

vm = program.to_vm()

vm_output = vm.run(input.detach().numpy())

torch.testing.assert_close(expected_output, torch.from_numpy(vm_output), atol = 1e-2, rtol = 1e-2)

print(f"latency (compute): {program.compute_duration_per_inference_us():.1f}us")

Streaming LSTM model

If you want the LSTM model to operate on an ongoing stream of data as its input sequence, it is probably

more desirable to use a streaming LSTM model. We can use the same PyTorch model defined above. The only additional

step required is to call the streaming_transform (detailed in Example 2: CNN) on the NNIR:

input_size = 128

hidden_size = 256

num_layers = 2

output_size = 16

model = LstmNet(input_size, hidden_size, num_layers, output_size)

seq_length = 20

input = torch.randn(seq_length, input_size)

# Trace the model's execution to annotate it with activation shapes

(model, expected_output) = vollo_torch.fx.prepare_shape(model, input)

nnir = vollo_torch.fx.nnir.to_nnir(model)

# We provide the streaming transform with the sequence axis to 'stream' over.

(nnir, output_streaming_axis) = nnir.streaming_transform(0)

assert(output_streaming_axis == 0)

Here, the streaming_transform tells the compiler to treat axis 0 as the sequence

dimension, and that we intend to provide the program with a single sequence element

per inference. I.e. on each inference, we pass in a tensor of size 128 and receive a

tensor of size 16 on each inference. The resulting Vollo program is stateful, and will

update the internal hidden state and cell state on each inference.

Note that this streaming model will have a much lower latency on Vollo than the non-streaming model.

The streaming model only needs to run num_layers = 2 LSTM operations per inference, where the non-streaming

model needs to run num_layers * seq_length = 2 * 20 LSTM operations per inference.

As above, we can now compile this streaming NNIR to a program with a chosen accelerator configuration, and test the program with a VM:

# Replace the Config in the line below with the Config for the accelerator you

# are using

program = nnir.to_program(vollo_compiler.Config.amd_v80_c6b32())

vm = program.to_vm()

vm_outputs = []

for i in range(seq_length):

# Note that the VM takes a single sequence element per run

vm_outputs.append(vm.run(input[i, :].detach().numpy()))

torch.testing.assert_close(

expected_output,

torch.stack(

[torch.from_numpy(output) for output in vm_outputs],

axis=output_streaming_axis,

),

atol = 1e-2,

rtol = 1e-2

)

print(f"latency (compute): {program.compute_duration_per_inference_us():.1f}us")

Resetting model state

When running a model, it can be reset to its initial state if it was compiled with

generate_state_reset = True. Note that this causes the program to use additional

resources, so may affect latency or cause the model to no longer fit.

program = nnir.to_program(vollo_compiler.Config.amd_v80_c6b32(), generate_state_reset=True)

See the Vollo RT Example for an example of how to then reset the model when running inferences.

Example 4: Mixed Precision

By default, operations on Vollo run in bfloat16 (BF16) format1, but there is support for some operations to be run in float32 (FP32) and for weights to be stored in 8-bit floating point (FP8, specifically E4M3).

FP32 Activations

See Supported Models for a list of which operations have FP32 support.

To run operations in FP32, the operations should be placed in a vollo_torch.Fp32Activations context. The following example

shows an MLP with some pre-processing on its inputs in FP32:

import torch

import torch.nn as nn

import torch.nn.functional as F

import vollo_torch

class PreprocessMLP(nn.Module):

def __init__(self, input_size, output_size, hidden_size):

super().__init__()

self.fc1 = nn.Linear(input_size, hidden_size)

self.fc2 = nn.Linear(hidden_size, hidden_size)

self.out = nn.Linear(hidden_size, output_size)

def forward(self, x, y):

with vollo_torch.Fp32Activations():

z = x + 0.763 * y

z = torch.clamp(z, -2.633, 2.633)

z = F.relu(self.fc1(z))

residual = z

z = F.relu(self.fc2(z)) + residual

return self.out(z)

input_size = 784

output_size = 10

hidden_size = 128

model = PreprocessMLP(input_size, output_size, hidden_size)

The inputs and outputs of a model can also be FP32. The default precision is BF16; if FP32 is required this must be

specified when calling to_nnir:

import vollo_compiler

inputs = [torch.randn(input_size), torch.randn(input_size)]

(model, expected_output) = vollo_torch.fx.prepare_shape(model, *inputs)

nnir = vollo_torch.fx.nnir.to_nnir(

model,

inputs_precisions = [vollo_compiler.NumberFormat.FP32, vollo_compiler.NumberFormat.FP32],

outputs_precisions = [vollo_compiler.NumberFormat.BF16]

)

# Note that the printed NNIR will be annotated with the precisions of each layer

# (See the activation_precision fields of the layers)

print(nnir)

Note that the model's inputs_precisions and outputs_precisions will determine what type of data format is sent/received between the Vollo runtime and the Vollo accelerator. If possible, it is best to make the precisions in the model match the

precisions of data you will be providing to the runtime. If these precisions do not match, the values will be converted in software

by the runtime, which can be slow.

config = vollo_compiler.Config.amd_v80_c6b32()

program = nnir.to_program(config)

FP8 Weights

Weight matrices of Linear, Conv1d, and LSTM operations can be stored in FP8 to halve the

amount of space used by them.

Note that FP8 is only used as the storage format, not the compute format; the weights are converted to BF16 before being used.

To use FP8 weights, the operations with FP8 weights should be placed in a vollo_torch.Fp8Weights

context. In the following example, the first two linear layers of the MLP will have their weights

stored in FP8, while the output layer will have its weights stored in BF16:

import torch

import torch.nn as nn

import torch.nn.functional as F

import vollo_torch

class Fp8MLP(nn.Module):

def __init__(self, input_size, output_size, hidden_size):

super().__init__()

self.fc1 = nn.Linear(input_size, hidden_size)

self.fc2 = nn.Linear(hidden_size, hidden_size)

self.out = nn.Linear(hidden_size, output_size)

def forward(self, x):

with vollo_torch.Fp8Weights():

x = F.relu(self.fc1(x))

residual = x

x = F.relu(self.fc2(x)) + residual

return self.out(x)

input_size = 784

output_size = 10

hidden_size = 128

model = Fp8MLP(input_size, output_size, hidden_size)

You can compile the model and print the program metrics to see that the model uses less space for weights than the BF16 version of the model in Example 1: MLP:

import vollo_compiler

input = torch.randn(input_size)

(model, expected_output) = vollo_torch.fx.prepare_shape(model, input)

nnir = vollo_torch.fx.nnir.to_nnir(model)

config = vollo_compiler.Config.amd_v80_c6b32()

program = nnir.to_program(config)

print(program.metrics())

Note that only constant weights can be stored in the FP8 format. To ensure predictable behaviour, whenever an Linear or MatMul with that requires dynamic weights is declared inside the context we reject it:

class UnsupportedDynamicMatMulInFP8(nn.Module):

def __init__(self):

super().__init__()

def forward(self, x):

with vollo_torch.Fp8Weights():

x = x @ torch.unsqueeze(x, 1)

return x

input_size = 784

model = UnsupportedDynamicMatMulInFP8()

import vollo_compiler

input = torch.randn(input_size)

(model, _expected_output) = vollo_torch.fx.prepare_shape(model, input)

nnir = vollo_torch.fx.nnir.to_nnir(model)

config = vollo_compiler.Config.amd_v80_c6b32()

try:

program = nnir.to_program(config, allow_dynamic_weights=True)

except Exception as e:

print(f"{e}")

else:

raise Exception("`to_program` expected to throw an exception")

This is true of most operations, however intermediate values in layer calculations are sometimes stored in higher precision, e.g. in the accumulation of dot products.

Example 5: Multiple Models in a Vollo Program

Vollo supports putting multiple models on a single accelerator.

Multiple NNIRs can be compiled into a single program:

import torch

import torch.nn as nn

import torch.nn.functional as F

import vollo_torch

class MLP(nn.Module):

def __init__(self, input_size, output_size, hidden_size):

super().__init__()

self.fc1 = nn.Linear(input_size, hidden_size)

self.fc2 = nn.Linear(hidden_size, hidden_size)

self.out = nn.Linear(hidden_size, output_size)

def forward(self, x):

x = F.relu(self.fc1(x))

residual = x

x = F.relu(self.fc2(x)) + residual

return self.out(x)

# Instantiate an MLP

input_size = 784

output_size = 10

hidden_size = 128

mlp_model = MLP(input_size, output_size, hidden_size)

mlp_input = torch.randn(input_size)

(mlp_model, mlp_expected_output) = vollo_torch.fx.prepare_shape(mlp_model, mlp_input)

mlp_nnir = vollo_torch.fx.nnir.to_nnir(mlp_model)

class CNN(nn.Module):

def __init__(self, in_channels, out_channels, hidden_channels, kernel_size=3):

super().__init__()

self.conv1 = vollo_torch.nn.PaddedConv1d(in_channels, hidden_channels, kernel_size)

self.conv2 = vollo_torch.nn.PaddedConv1d(hidden_channels, out_channels, kernel_size)

def forward(self, x):

x = F.relu(self.conv1(x))

x = F.relu(self.conv2(x))

return x

# Instantiate a CNN

in_channels = 32

out_channels = 1

hidden_channels = 128

cnn_model = CNN(in_channels, out_channels, hidden_channels)

batch_size = 1

sequence_length = 5

cnn_input = torch.randn(batch_size, in_channels, sequence_length)

(cnn_model, cnn_expected_output) = vollo_torch.fx.prepare_shape(cnn_model, cnn_input)

cnn_nnir = vollo_torch.fx.nnir.to_nnir(cnn_model)

(cnn_nnir, output_axis) = cnn_nnir.streaming_transform(2)

# Compile the multi-model program

import vollo_compiler

# Replace the Config in the line below with the Config for the accelerator you

# are using

program_builder = vollo_compiler.ProgramBuilder(vollo_compiler.Config.amd_v80_c6b32())

program_builder.add_nnir(mlp_nnir)

program_builder.add_nnir(cnn_nnir)

multi_model_program = program_builder.to_program()

The vollo_compiler.ProgramBuilder allows you to create a multi-model program. Building a multi-model program may give an allocation error if

the models can't fit on the given Config. Generally each individual model will only have a small latency overhead compared to running it as an individual program. This overhead comes from selecting which model to run.

A model_index can be provided when running inferences on the accelerator or on the VM. The models appear in the order in which they were added to the ProgramBuilder. For example on the VM:

vm = multi_model_program.to_vm()

mlp_vm_output = vm.run(mlp_input.detach().numpy(), model_index = 0)

torch.testing.assert_close(mlp_expected_output, torch.from_numpy(mlp_vm_output), atol = 1e-2, rtol = 1e-2)

cnn_vm_outputs = []

for i in range(5):

cnn_vm_outputs.append(vm.run(cnn_input[:, :, i].detach().numpy(), model_index = 1))

torch.testing.assert_close(

cnn_expected_output,

torch.stack(

[torch.from_numpy(output) for output in cnn_vm_outputs],

axis=output_axis,

),

atol = 1e-2,

rtol = 1e-2

)

The data dimension

For a model to compile on Vollo, in addition to the normal tensor rank/extent constraints on algorithms/functions, an additional constraint on the data dimension must be satisfied. Conceptually, the data dimension is the contiguous dimension of a tensor, it transforms and constrains algorithms according to the rules below.

In most use cases the data dimension is completely opaque, the Vollo compiler will deduce it and the program will compile without changes.

For the remainder of this page:

- We represent an

n-dimensional (a.k.a. rank-n) tensors as[a b! c], in this example a rank-3 tensor with extentsa,band,c. - The dimension with a

!is the data dimension. - Tensors that are compile-time constants (like weights) don't have a data dimension.

Pointwise

Shape and data dimension must match.

[a b! c] (*) [a b! c] -> [a b! c]

Where (*) is any pointwise operation, e.g. +, -, *, /, maximum,

minimum, the pointwise overload of max and min, etc.

Slicing

This preserves the data dimension.

A slice on the data dimension:

[a b c!][:, :, :n] -> [a b n!]

Non data-dimension slice:

[a b! c][:, :, :n] -> [a b! n]

A non data-dimension slice is free (no compute).

Unsqueeze (a.k.a. new-axis)

You can add a new axis anywhere, the new axis is never the data dimension:

[a! b].unsqueeze(dim=0) -> [1 a! b]

Broadcasting

You can broadcast along a non data-dimension:

[1 b!] -> [n b!]

Or along the data dimension:

[a 1!] -> [a n!]

Broadcasting a non data-dimension is free (no compute), and broadcasting the data dimension is close to free.

Concatenation

Similar to a pointwise operation, shape and data dimension of each concatenated tensor must match.

Along the data dimension:

[a! b c].repeat(n, dim=0) -> [(a * n)! b c]

Non data-dimension:

[a! b c].repeat(n, dim=1) -> [a! (b * n) c]

A non data-dimension concatenation is free (no compute).

Note: stacking is the same but with a new-axis before the concatenation.

Reduction

In general reductions preserve the position of the data dimension.

Along the data dimension:

[a! b].sum(dim=0) -> [1! b]

Non data-dimension reduction (generally slower):

[a! b].sum(dim=1) -> [a!]

Note: keepdim must be used in the former and is optional in the latter.

Matrix multiplication

These operations transform the data dimension in non-obvious ways, here we use

* do denote any number of commensurate broadcast dimensions, none of which

are allowed to be the data dimension.

With one side a compile-time constant, in this case the LHS (WLOG):

[* i j] @ [* j! k] -> [* i! k]

That is, the data dimension must be along the contracted dimension of the runtime tensor. The output data dimension is along the "replaced" index.

Note: a linear layer is a special case of the above with the k dimension

squeezed out.

If the contraction is not along the data dimension of the non-constant

(requires allow_dynamic_weights):

[* i j] @ [* j k!] -> [* i k!]

That is, the data dimension of non-constant is preserved in the output. This potentially has a higher latency and consumes more tensor RAM than contracting along the data dimension.

With both sides runtime tensors (also requires allow_dynamic_weights):

[* i! j] @ [* j! k] -> [* i! k]

That is, the contracted dimension must be the data dimension of exactly one of the input tensors (in this case the RHS WLOG). The output data dimension is that of the side whose data dimension was not contracted, for example:

[* i j!] @ [* j k!] -> [* i k!]

This uses more tensor RAM and potentially has a higher latency than contractions with a constant.

Transpose

Tensors can be transposed without restriction. If one of the transposed dimensions is the data dimension, the data dimension is transposed to that dimension:

[a! b c d].transpose(0, 2) -> [c b a! d]

Reshape

For a given tensor's extents, e.g. [a b c], each dimension has a stride equal

to the product of all dimensions to its right, i.e. [(b * c) c 1]. The stride

of the data dimension must/will be preserved during a reshape. For example:

[a! (b * c)] -> [a! b c]

Is valid because the stride of the data dimension is b * c before and after.

[a b c!] -> [b a c!]

Is valid because the stride of the data dimension is 1 before and after.

[a b! c] -> [(a * b)! c]

Is valid because the stride of the data dimension is c before and after, similarly:

[a (n * b)! c] -> [a n b! c]

Note: that the resultant data dimension is deduced to b! rather than n! to

uphold the stride requirement.

However:

[a b! c] -> [a (b * c)!]

Is invalid because the stride of the data dimension is c before but 1 after.

If the output shape has multiple candidate dimensions with the input data dimension's stride (note that these candidate dimensions are all consecutive and all but the leftmost have extent 1), the leftmost of them will be chosen as the output data dimension:

[a! b] -> [a! 1 b]

A reshape that doesn't change the extent of the data dimension is free (no compute).

Note: the strides discussed in this subsection are conceptual and not related to the strides of the tensors queryable from PyTorch etc.

ONNX Support

Vollo also provides a tool for compiling ML models defined in ONNX.

vollo-onnx is a command line tool which allows the user to specify an input ONNX file and produces a .vollo program as output. The user specifies a path to the input .onnx file:

Arguments:

<INPUT>

Path to the input .onnx file

The user can specify:

-

The output path:

-o, --output <OUTPUT> Output path for the compiled program file [default: program.vollo] -

A name for the model:

--model-name <MODEL_NAME> Name of the model -

The hardware configuration to use based on a JSON file (this JSON file can be generated using the

Configmethodsavein thevollo_compilerpython module):--hw-config <HW_CONFIG_JSON> Path to the hardware config JSON file -

A name for the hardware configuration to use (from a set of preset configs).

--hw-config-preset <PRESET_NAME> Hardware configuration to use, chosen from a set of presets [possible values: ia420f-c6b32, ia840f-c3b64, ia840f-c2b64d, v80-c6b32] -

Which transformations to perform on the model. Currently the only available transformation is the streaming transform Example 2: CNN:

--streaming-transform <STREAMING_AXIS>... Axes on which to perform the streaming transform in the NNIR graph There should be one axis per model input, as separate arguments If unspecified, no streaming transform is performed Example: --streaming-transform 0 1 for a two-input model with input streaming axes 0 and 1 -

The input shapes of the model. This is required if the ONNX model has dynamic input shapes. Vollo requires that the shapes of the inputs be known at compile-time:

--override-input-shapes <SHAPE>... If the model has dynamic input shapes, the user must pass fixed input shapes Separate each dimension with a ',' and pass each model input as a separate argument Example: --override-input-shapes 10,100,250 20,40 for a two-input model with input shapes (10, 100, 250) and (20, 40) -

Whether to elide all compute logic and generate a program with only IO logic. This is useful for determining IO latencies.

--io-only Generate a program with IO only - useful for testing IO latencies -

Whether to disable certain optimizations in the compiler which increase compilation time.

--disable-optimizations Disables some compiler optimizations. This can improve compilation time

Simplifying ONNX Models

vollo-onnx has a limited list of supported ONNX nodes. Often ONNX models can be over-complicated, and contain unnecessary shaping operations. It is recommended that onnx-simplifier be used before calling vollo-onnx on an ONNX model to remove these unnecessary shaping operations which aren't supported by vollo-onnx:

onnx-sim <model.onnx> <model-sim.onnx> --overwrite-input-shape <model-input-shape>

It is also recommended to use the --overwrite-input-shape with onnx-simplifier, as this can enable further simplifications and better constant folding.

Using ONNX from Python

ONNX models can also be imported and translated to NNIR models directly in python using the static NNIR method from_onnx. This also requires that the input shapes be specified if the ONNX model has dynamic input shapes, otherwise it can be None.

onnx_nnir = vollo_compiler.NNIR.from_onnx(onnx_path, input_shapes)

Supported Nodes

Tensors are expected to be in float32 format, unless they are used as indices / axes (in which case they should be int64s).

vollo-onnx supports models with the following nodes:

| Operator | Support Notes |

|---|---|

| Pointwise arithmetic ops | Add, Sub, Mul, Div |

| Inequality | >, <, >=, <= (when followed by a Where) |

Max and Min | |

Neg | |

| Clamp ops | Clip, Relu |

| Matrix multiplication | MatMul / Gemm where one input is a constant |

Conv | 1d with left-padding such that input and output seq dimensions match, groups == 1 or groups == in_channels == out_channels |

LSTM | LSTM without explicit hidden or cell state initialisation |

Gather | With a 0d/1d tensor of indices |

Slice | step size 1 with constant starts, ends and axes. |

ReduceSum, ReduceMean | With constant axes, keepdims = 1 required on data dimension |

Where | If the Where condition is an inequality comparison |

Concat | |

Transpose | See [data dimension][data-dimension.md) |

Softmax | |

LayerNormalization | With axis = -1. Supported in onnx opset versions >= 17 |

BatchNormalization | Where input scale, bias, mean and var are constants |

Squeeze, Unsqueeze | |

Reciprocal | |

Identity | |

Sqrt | |

Tanh | |

Exp | |

Softplus | |

Sigmoid | |

Expand | |

Reshape | The stride of the data dimension must be unchanged |

Benchmarks

This section provides benchmarks for the Vollo accelerator for a variety of models.

Performance figures are given for the following configurations of the Vollo accelerator:

- a 6 core, block size 32 configuration which is provided for the V80 accelerator card

- a 3 core, block size 64 configuration which is provided for the IA-840F accelerator card

- a 6 core, block size 32 configuration which is provided for the IA-420F accelerator card

If you require a different configuration, please contact us at vollo@myrtle.ai.

All these performance numbers can be measured using the vollo-sdk with the correct accelerator card

by running the provided benchmark script.

We also provide performance figures for a PCIe roundtrip for various input and output sizes.

Multilayer perceptron (MLP)

The model below is a simple multilayer perceptron (MLP) with 3 layers.

class MLP(nn.Module):

def __init__(self, input_size, hidden_size, output_size):

super().__init__()

self.fc1 = nn.Linear(input_size, hidden_size)

self.fc2 = nn.Linear(hidden_size, hidden_size)

self.fc3 = nn.Linear(hidden_size, output_size)

def forward(self, x):

x = nn.functional.relu(self.fc1(x))

x = nn.functional.relu(self.fc2(x))

return self.fc3(x)

mlp = MLP(256.0, 384.0, 128.0)

We demonstrate the model at a variety of batch sizes. The model has 295K parameters.

V80: 6 cores, block size 32

| Model | Batch size | Mean latency (us) | 99th percentile latency (us) |

|---|---|---|---|

| mlp_b1 | 1 | 1.5 | 1.8 |

| mlp_b4 | 4 | 1.9 | 2.2 |

| mlp_b8 | 8 | 2.7 | 2.9 |

IA-840F: 3 cores, block size 64

| Model | Batch size | Mean latency (us) | 99th percentile latency (us) |

|---|---|---|---|

| mlp_b1 | 1 | 1.8 | 1.9 |

| mlp_b4 | 4 | 2.4 | 2.5 |

| mlp_b8 | 8 | 3.4 | 3.6 |

IA-420F: 6 core, block size 32

| Model | Batch size | Mean latency (us) | 99th percentile latency (us) |

|---|---|---|---|

| mlp_b1 | 1 | 1.8 | 2.0 |

| mlp_b4 | 4 | 2.8 | 2.9 |

| mlp_b8 | 8 | 4.1 | 4.3 |

1D Convolutional neural networks (CNN)

We benchmark a simple 1-D convolutional model with a residual connection after every layer.

class ConvBlock(nn.Module):

def __init__(self, channels, kernel_size):

super().__init__()

self.conv = vollo_torch.nn.PaddedConv1d(channels, channels, kernel_size)

def forward(self, inp):

x = self.conv(inp)

return nn.functional.relu(x) + inp

class CNN(nn.Module):

def __init__(self, num_layers, kernel_size, channels):

super().__init__()

assert num_layers >= 1

self.cnn = nn.Sequential(

*[ConvBlock(channels, kernel_size) for i in range(num_layers)],

)

def forward(self, x):

x = self.cnn(x) # N x channels x T

return x

The kernel size for all models is 8. The batch size and sequence length are both set to 1 (i.e., we benchmark a single timestep). Consecutive inferences are run with spacing between them to minimise latency.

V80: 6 cores, block size 32

| Model | Layers | Channels | Parameters | Mean latency (us) | 99th percentile latency (us) |

|---|---|---|---|---|---|

| cnn_tiny | 3 | 128 | 393K | 1.5 | 1.8 |

| cnn_small | 3 | 256 | 1.6M | 1.8 | 2.0 |

| cnn_med | 6 | 256 | 3.1M | 2.4 | 2.7 |

IA-840F: 3 cores, block size 64

| Model | Layers | Channels | Parameters | Mean latency (us) | 99th percentile latency (us) |

|---|---|---|---|---|---|

| cnn_tiny | 3 | 128 | 393K | 1.7 | 1.8 |

| cnn_small | 3 | 256 | 1.6M | 1.9 | 2.0 |

| cnn_med | 6 | 256 | 3.1M | 2.5 | 2.5 |

IA-420F: 6 cores, block size 32

| Model | Layers | Channels | Parameters | Mean latency (us) | 99th percentile latency (us) |

|---|---|---|---|---|---|

| cnn_tiny | 3 | 128 | 393K | 1.7 | 1.9 |

| cnn_small | 3 | 256 | 1.6M | 2.0 | 2.1 |

| cnn_med | 6 | 256 | 3.1M | 2.8 | 2.9 |

Long Short Term Memory (LSTM) networks

We benchmark an LSTM model consisting of a stack of LSTMs followed by a linear layer.

class LSTM(nn.Module):

def __init__(self, num_layers, input_size, hidden_size, output_size):

super().__init__()

assert num_layers >= 1

self.lstm = vollo_torch.nn.LSTM(

input_size, hidden_size, num_layers=num_layers

)

self.fc = nn.Linear(hidden_size, output_size)

def forward(self, x):

x = self.lstm(x)

x = self.fc(x)

return x

For all the benchmarked models, the input size is the same as the hidden size for all models and the output size is set to 32. The layers refers to the number of LSTM layers in the stack. The batch size and sequence length are both set to 1 (i.e., we benchmark a single timestep). Consecutive inferences are run with spacing between them to minimise latency.

We have also had LSTM models benchmarked and audited as part of a STAC-ML submission where we held the lowest latency across all models. Please refer to our STAC-ML submissions for more details:

Note that Vollo's current performance, as shown in the tables below, is significantly improved over the STAC-ML submissions.

V80: 6 core, block size 32

| Model | Layers | Hidden size | Parameters | Mean latency (us) | 99th percentile latency (us) |

|---|---|---|---|---|---|

| lstm_tiny | 2 | 128 | 268K | 1.4 | 1.4 |

| lstm_small | 3 | 256 | 1.6M | 2.0 | 2.0 |

| lstm_med | 3 | 480 | 5.6M | 3.2 | 3.2 |

| lstm_med_deep | 6 | 320 | 4.9M | 3.3 | 3.4 |

| lstm_large | 3 | 960 | 22.2M | 7.3 | 7.4 |

IA-840F: 3 core, block size 64

| Model | Layers | Hidden size | Parameters | Mean latency (us) | 99th percentile latency (us) |

|---|---|---|---|---|---|

| lstm_tiny | 2 | 128 | 268K | 1.7 | 1.8 |

| lstm_small | 3 | 256 | 1.6M | 2.1 | 2.2 |

| lstm_med | 3 | 480 | 5.6M | 2.7 | 2.9 |

| lstm_med_deep | 6 | 320 | 4.9M | 3.1 | 3.2 |

The large model is not supported on the IA-840F accelerator card as it is too large to fit in the accelerator memory.

IA-420F: 6 core, block size 32

| Model | Layers | Hidden size | Parameters | Mean latency (us) | 99th percentile latency (us) |

|---|---|---|---|---|---|

| lstm_tiny | 2 | 128 | 268K | 1.7 | 1.8 |

| lstm_small | 3 | 256 | 1.6M | 2.3 | 2.4 |

The medium and large models are not supported on the IA-420F accelerator card as they are too large to fit in the accelerator memory.

IO Round Trip

The following IO round trip times are sampled by using a program with no compute on the Vollo accelerator from the Vollo runtime.

More specifically this Vollo accelerator program waits for the last input byte to arrive before it sends the first output byte back. This method takes into account some of the overheads (such as copying to the DMA buffer in the Vollo runtime) associated with IO and this test is set up to see how it scales with difference sizes of inputs and outputs.

The following tables shows the round trip times in μs on the V80 board (similar times

were observed on other boards), for different input and output sizes. Using fewer than

64 bytes gives the same times as 64 bytes.

To reproduce these values on your own hardware run the provided benchmark

script with environment variable RUN_IO_TEST=1.

User buffers

This includes copying data to/from DMA buffers.

mean:

| out\in | 64 B | 128 B | 256 B | 512 B | 1024 B | 2048 B | 4096 B | 8192 B | 16384 B |

|---|---|---|---|---|---|---|---|---|---|

| 64 B | 1.47 | 1.49 | 1.54 | 1.55 | 1.61 | 1.69 | 1.93 | 2.15 | 2.77 |

| 128 B | 1.54 | 1.54 | 1.59 | 1.65 | 1.74 | 1.75 | 1.93 | 2.28 | 2.90 |

| 256 B | 1.60 | 1.63 | 1.68 | 1.69 | 1.85 | 1.88 | 1.94 | 2.30 | 2.91 |

| 512 B | 1.70 | 1.74 | 1.76 | 1.87 | 1.93 | 1.93 | 2.06 | 2.32 | 2.96 |

| 1024 B | 1.71 | 1.85 | 1.80 | 1.87 | 1.93 | 1.93 | 2.08 | 2.42 | 3.01 |

| 2048 B | 1.84 | 1.92 | 1.93 | 1.93 | 1.93 | 2.01 | 2.17 | 2.45 | 3.10 |

| 4096 B | 2.01 | 2.05 | 2.09 | 2.13 | 2.20 | 2.31 | 2.39 | 2.68 | 3.38 |

| 8192 B | 2.51 | 2.53 | 2.58 | 2.58 | 2.62 | 2.66 | 2.90 | 3.20 | 3.88 |

| 16384 B | 3.45 | 3.44 | 3.51 | 3.55 | 3.67 | 3.72 | 3.81 | 3.89 | 4.83 |

p99:

| out\in | 64 B | 128 B | 256 B | 512 B | 1024 B | 2048 B | 4096 B | 8192 B | 16384 B |

|---|---|---|---|---|---|---|---|---|---|

| 64 B | 1.75 | 1.77 | 1.70 | 1.81 | 1.78 | 1.95 | 2.07 | 2.31 | 2.92 |

| 128 B | 1.71 | 1.79 | 1.90 | 1.91 | 1.97 | 2.05 | 2.13 | 2.52 | 3.11 |

| 256 B | 1.87 | 1.94 | 1.97 | 1.99 | 2.00 | 2.08 | 2.15 | 2.54 | 3.09 |

| 512 B | 1.94 | 1.98 | 1.99 | 2.00 | 2.00 | 2.10 | 2.32 | 2.50 | 3.26 |

| 1024 B | 2.03 | 2.00 | 2.02 | 2.04 | 2.08 | 2.11 | 2.33 | 2.73 | 3.28 |

| 2048 B | 2.09 | 2.08 | 2.10 | 2.08 | 2.06 | 2.28 | 2.44 | 2.71 | 3.35 |

| 4096 B | 2.29 | 2.32 | 2.35 | 2.38 | 2.44 | 2.52 | 2.67 | 2.96 | 3.65 |

| 8192 B | 2.75 | 2.92 | 2.77 | 2.79 | 3.10 | 3.16 | 3.08 | 3.64 | 4.13 |

| 16384 B | 3.83 | 3.83 | 3.87 | 3.91 | 3.92 | 4.04 | 4.15 | 4.20 | 5.35 |

Raw DMA buffers

This is using buffers allocated with vollo_rt_get_raw_buffer which lets the runtime skip IO copy.

mean:

| out\in | 64 B | 128 B | 256 B | 512 B | 1024 B | 2048 B | 4096 B | 8192 B | 16384 B |

|---|---|---|---|---|---|---|---|---|---|

| 64 B | 1.45 | 1.48 | 1.54 | 1.54 | 1.59 | 1.66 | 1.93 | 2.15 | 2.76 |

| 128 B | 1.47 | 1.49 | 1.54 | 1.54 | 1.59 | 1.66 | 1.93 | 2.15 | 2.76 |

| 256 B | 1.53 | 1.54 | 1.54 | 1.57 | 1.61 | 1.71 | 1.93 | 2.15 | 2.77 |

| 512 B | 1.54 | 1.56 | 1.61 | 1.64 | 1.66 | 1.75 | 1.93 | 2.21 | 2.83 |

| 1024 B | 1.59 | 1.61 | 1.65 | 1.66 | 1.72 | 1.78 | 1.93 | 2.22 | 2.90 |

| 2048 B | 1.66 | 1.66 | 1.72 | 1.74 | 1.78 | 1.93 | 2.01 | 2.32 | 2.91 |

| 4096 B | 1.88 | 1.93 | 1.93 | 1.93 | 1.93 | 2.00 | 2.15 | 2.45 | 3.09 |

| 8192 B | 2.08 | 2.12 | 2.15 | 2.15 | 2.21 | 2.26 | 2.42 | 2.77 | 3.35 |

| 16384 B | 2.65 | 2.69 | 2.71 | 2.77 | 2.77 | 2.91 | 3.00 | 3.33 | 3.92 |

p99:

| out\in | 64 B | 128 B | 256 B | 512 B | 1024 B | 2048 B | 4096 B | 8192 B | 16384 B |

|---|---|---|---|---|---|---|---|---|---|

| 64 B | 1.73 | 1.75 | 1.74 | 1.67 | 1.85 | 1.83 | 2.10 | 2.38 | 2.98 |

| 128 B | 1.74 | 1.75 | 1.71 | 1.67 | 1.85 | 1.89 | 2.10 | 2.37 | 2.97 |

| 256 B | 1.78 | 1.77 | 1.64 | 1.84 | 1.76 | 1.99 | 2.06 | 2.38 | 2.94 |

| 512 B | 1.61 | 1.84 | 1.80 | 1.91 | 1.75 | 2.02 | 2.02 | 2.44 | 3.10 |

| 1024 B | 1.85 | 1.82 | 1.88 | 1.77 | 1.97 | 2.04 | 1.99 | 2.60 | 3.11 |

| 2048 B | 1.74 | 1.94 | 1.94 | 2.02 | 2.05 | 2.07 | 2.28 | 2.54 | 3.01 |

| 4096 B | 2.09 | 2.08 | 2.05 | 2.04 | 2.00 | 2.28 | 2.34 | 2.71 | 3.35 |

| 8192 B | 2.29 | 2.40 | 2.33 | 2.34 | 2.46 | 2.42 | 2.55 | 2.92 | 3.63 |

| 16384 B | 2.90 | 2.96 | 2.92 | 2.95 | 2.92 | 3.10 | 3.28 | 3.50 | 4.20 |

MMIO

This is skipping DMA for the input (raw DMA buffers are used for the output).

It is configured via the VOLLO_MMIO_MAX_SIZE environment variable.

mean:

| out\in | 64 B | 128 B | 256 B | 512 B | 1024 B | 2048 B | 4096 B | 8192 B | 16384 B |

|---|---|---|---|---|---|---|---|---|---|

| 64 B | 0.89 | 0.89 | 0.88 | 0.91 | 0.97 | 1.09 | 1.35 | 1.85 | 2.88 |

| 128 B | 0.89 | 0.90 | 0.89 | 0.91 | 0.98 | 1.11 | 1.36 | 1.87 | 2.89 |

| 256 B | 0.91 | 0.92 | 0.91 | 0.94 | 1.01 | 1.13 | 1.39 | 1.89 | 2.91 |

| 512 B | 0.98 | 0.97 | 0.98 | 0.99 | 1.06 | 1.19 | 1.44 | 1.94 | 2.97 |

| 1024 B | 1.00 | 1.01 | 1.00 | 1.03 | 1.09 | 1.22 | 1.48 | 1.98 | 3.00 |

| 2048 B | 1.07 | 1.08 | 1.09 | 1.10 | 1.17 | 1.29 | 1.55 | 2.05 | 3.07 |

| 4096 B | 1.22 | 1.22 | 1.23 | 1.24 | 1.31 | 1.43 | 1.68 | 2.19 | 3.22 |

| 8192 B | 1.49 | 1.50 | 1.50 | 1.52 | 1.58 | 1.72 | 1.97 | 2.49 | 3.51 |

| 16384 B | 2.07 | 2.07 | 2.08 | 2.10 | 2.17 | 2.29 | 2.55 | 3.06 | 4.09 |

p99:

| out\in | 64 B | 128 B | 256 B | 512 B | 1024 B | 2048 B | 4096 B | 8192 B | 16384 B |

|---|---|---|---|---|---|---|---|---|---|

| 64 B | 0.91 | 0.90 | 0.90 | 0.92 | 0.98 | 1.10 | 1.37 | 1.86 | 2.90 |

| 128 B | 0.91 | 0.91 | 0.91 | 0.93 | 0.99 | 1.11 | 1.37 | 1.88 | 2.91 |

| 256 B | 0.93 | 0.93 | 0.93 | 0.95 | 1.02 | 1.14 | 1.40 | 1.90 | 2.93 |

| 512 B | 1.00 | 0.99 | 0.99 | 1.01 | 1.07 | 1.20 | 1.46 | 1.96 | 2.98 |

| 1024 B | 1.02 | 1.02 | 1.02 | 1.04 | 1.10 | 1.23 | 1.49 | 1.99 | 3.02 |

| 2048 B | 1.09 | 1.09 | 1.11 | 1.12 | 1.18 | 1.31 | 1.56 | 2.06 | 3.10 |

| 4096 B | 1.24 | 1.24 | 1.25 | 1.25 | 1.32 | 1.44 | 1.70 | 2.21 | 3.24 |

| 8192 B | 1.51 | 1.51 | 1.51 | 1.53 | 1.60 | 1.73 | 1.98 | 2.50 | 3.53 |

| 16384 B | 2.09 | 2.09 | 2.09 | 2.11 | 2.18 | 2.31 | 2.56 | 3.08 | 4.11 |

Setting up the Vollo accelerator

This section describes how to program your accelerator card with the Vollo Accelerator upon first use and how to reprogram your accelerator card with updated versions of the Vollo Accelerator. It also describes how to obtain a Vollo license which you will need to use the Vollo accelerator.

Environment Variable Setup

The initial setup instructions should be run in the Vollo SDK directory.

cd vollo-sdk-<VERSION>

When using Vollo, you should also have the setup.sh script sourced in bash

to set up environment variables used by Vollo:

source setup.sh

System Requirements

CPU Requirements

An x86-64 CPU is required to run the Vollo runtime.

Accelerator Card Requirements

The SDK runs on a server CPU with PCIe FPGA accelerator cards. It currently supports the following accelerator cards:

| Accelerator Card | FPGA | Max parameter count |

|---|---|---|

| BittWare IA-420f | Intel Agilex AGF014 | 3.1 Million |

| BittWare IA-840f | Intel Agilex AGF027 | 8.4 Million |

| Napatech NT400D11 | Intel Agilex AGF014 | 3.1 Million |

| AMD Alveo V80 | AMD Versal XCV80 | 25.2 Million1 |

Operating System Requirements

Vollo is compatible with Ubuntu 20.04 and later.

50.3 Million if using FP8 weights.

Programming the Agilex FPGA

This section assumes that the Vollo SDK is already installed and setup on the machine that you are using. If you haven't done so already, instructions for how to do that may be found at: Vollo SDK Installation.

Make sure the VOLLO_SDK environment variable is set by sourcing setup.sh from the Vollo SDK.

source <path-to-VOLLO_SDK>/setup.sh

Download the bitstream for your FPGA

The bitstream is available on the Github Release page alongside the Vollo SDK.

For example to download the bitstream for the Agilex ia840f board with the c2b64d configuration of Vollo:

curl -LO https://github.com/MyrtleSoftware/vollo-sdk/releases/download/v27.1.0/vollo-bittware-ia840f-c2b64d-27.1.tar.gz

mkdir -p $VOLLO_SDK/bitstream

tar -xzf vollo-bittware-ia840f-c2b64d-27.1.tar.gz -C $VOLLO_SDK/bitstream

The Agilex-based boards that are currently supported are:

-

Bittware IA420F

-

Bittware IA840F

-

Napatech NT400D11 (Link programmable version)

Note on programming the Napatech NT400D11 over JTAG

The NT400D11 card needs additional cabling beyond a USB cable to program the board over JTAG. This cabling is provided as a development kit by Napatech (PGM-DEVKIT-IFPGA-DF52-2XIDC-UART, product number: 802-0116-01-10) and includes:

-

An Intel® FPGA USB-Blaster II cable and,

-

A Napatech Passive FPGA Download Cable converter box

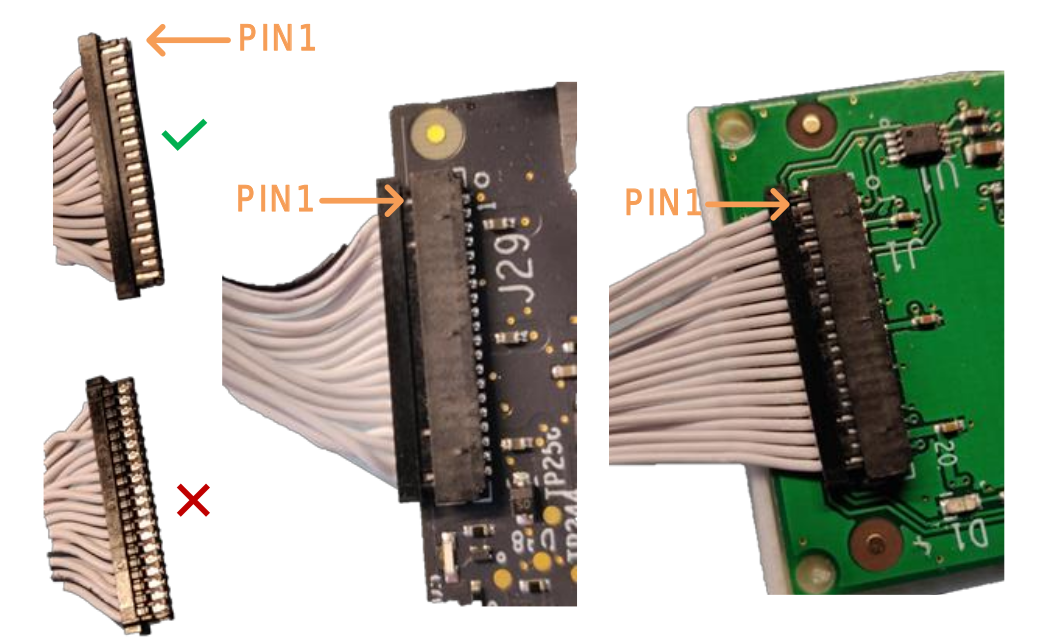

These two cables must be connected to each other as shown in the image below:

To connect this cable array to the Napatech board, the long thin plug should be connected to the connector shown in the following image:

In order to correctly couple these two connectors, observe the conventions shown in the following image:

Connector the USB side of the cable array to a high-speed USB port on your host PC and the follow the rest of the directions in the next section.

Programming the FPGA via JTAG

If your FPGA is not already programmed with the Vollo accelerator then please follow these instructions to load the bitstream into the accelerator card's flash memory.

This requires a USB cable to be connected to the accelerator card and Quartus programmer to be installed on the system so that the device can be programmed over JTAG.

If the FPGA card already has a Vollo Accelerator Bitstream, it can be updated over PCIe by following the steps in the section Program the FPGA via PCIe below. Note that you only need to update the bitstream if updating to an incompatible version of the Vollo SDK. Programming over PCIe is faster than programming over JTAG, and does not require a USB programming cable or for Quartus Programmer to be installed.

-

Download and install the latest Quartus Programmer:

- Navigate to https://www.intel.com/content/www/us/en/software-kit/782411/intel-quartus-prime-pro-edition-design-software-version-23-2-for-linux.html.

- Select

Additional Softwareand scroll down to find the Programmer. - Follow the instructions for installation.

-

Add Quartus programmer to your path:

export QUARTUS_DIR=<path to qprogrammer install> export PATH=$QUARTUS_DIR/qprogrammer/quartus/bin:$PATH -

Start the jtag daemon:

sudo killall jtagd sudo jtagd -

Run

jtagconfigfrom the Quartus install, you should see the device(s):$ jtagconfig 1) IA-840F [1-5.2] 0341B0DD AGFB027R25A(.|R0)or, for the NT400D11:

$ jtagconfig 1) USB-BlasterII [1-5] C34320DD AGFA014R24C(.|B|AA) -

Navigate to the directory containing the

jicfile:cd $VOLLO_SDK/bitstream -

Set the JTAG clock frequency of the device you want to program to 16 MHz. Specify the device by providing the name returned by

jtagconfig:jtagconfig --setparam "IA-840F [1-5.2]" JtagClock 16Mor, for the NT400D11:

jtagconfig --setparam "USB-BlasterII [1-5]" JtagClock 16M -

Start the programming operation on the chosen device. This takes around 20 minutes. For the IA840F:

quartus_pgm -c "IA-840F [1-5.2]" -m JTAG -o "ipv;vollo-bittware-ia840f-c3b64.jic"or, for the IA420F:

quartus_pgm -c "IA-420F [1-5.2]" -m JTAG -o "ipv;vollo-bittware-ia420f-c6b32.jic"or, for the NT400D11:

quartus_pgm -c "USB-BlasterII [1-5]" -m JTAG -o "ipv;vollo-napatech-nt400d11-c6b32.jic" -

Go back to 6 and program any other devices.

-

Power off the system and start it back up. The bitstream will now be loaded onto the FPGA.

For the configuration process to be triggered the board has to register the power being off. It is recommended to turn the power off and then wait a few seconds before turning the power back on to ensure this happens. -

Check a Vollo bitstream is loaded:

$ lspci -d 1ed9:766f 51:00.0 Processing accelerators: Myrtle.ai Device 766f (rev 01)Check the correct Vollo bitstream is loaded:

vollo-tool bitstream-check bitstream/<bitstream-name>.json

Programming the FPGA via PCIe

NOTE: this can only be done with an FPGA that is already programmed with a Vollo bitstream.

-

Load the kernel driver:

sudo ./load-kernel-driver.sh -

Check the current bitstream information:

source setup.sh vollo-tool bitstream-info -

Check that the device is set up for remote system updates by running the command below, with

device indexrepresenting the index of the device you want to update, in the order shown in the previous command, starting from 0. It should print ajsonstring to the terminal showing the device status.vollo-tool fpga-config rsu-status <device index> -

Update the

USER_IMAGEpartition of the flash with the new bitstream image contained in therpdarchive in the$VOLLO_SDK/bitstreamdirectory. This should take around 5 minutes. Do not interrupt this process until it completes.sudo ./load-kernel-driver.sh vollo-tool fpga-config overwrite-partition <device index> <.rpd.tar.gz file> USER_IMAGE -

Repeat step 4 for any other devices you wish to update.

-

Power off the system and start it back up.

For the configuration process to be triggered the board has to register the power being off. It is recommended to turn the power off and then wait a few seconds before turning the power back on to ensure this happens. -

Repeat steps 1, 2 and 3. The

bitstream-infocommand should show that the updated bitstream has been loaded (e.g. a newer release date), and the output of thersu-statuscommand should show all zeroes for theerror_codeandfailing_image_addressfields. -

Check the correct Vollo bitstream is loaded:

sudo ./load-kernel-driver.sh vollo-tool bitstream-check bitstream/<bitstream-name>.json

Programming the Artena FPGA

This section assumes that the Vollo SDK is already installed and setup on the machine that you are using. If you haven't done so already, instructions for how to do that may be found at: Vollo SDK Installation

Make sure the VOLLO_SDK environment variable is set by sourcing setup.sh from the Vollo SDK.

source <path-to-VOLLO_SDK>/setup.sh

Download the bitstream for your FPGA

The bitstream is available on the Github Release page alongside the Vollo SDK. For example to

download the bitstream for the Silicom Artena board with the c8b32 configuration of Vollo:

curl -LO https://github.com/MyrtleSoftware/vollo-sdk/releases/download/v27.1.0/vollo-silicom-artena-c8b32-27.1.tar.gz

mkdir -p $VOLLO_SDK/bitstream

tar -xzf vollo-silicom-artena-c8b32-27.1.tar.gz -C $VOLLO_SDK/bitstream

An LSTM-only image is available for the Artena which runs at a slightly higher clock frequency than the full-featured-Vollo c8b32 version. This may be downloaded as follows:

curl -LO https://github.com/MyrtleSoftware/vollo-sdk/releases/download/v27.1.0/vollo-silicom-artena-c8b32lstm-27.1.tar.gz

mkdir -p $VOLLO_SDK/bitstream

tar -xzf vollo-silicom-artena-c8b32lstm-27.1.tar.gz -C $VOLLO_SDK/bitstream

Programming the FPGA via JTAG

Programming an Artena board over JTAG is necessary if the board does not yet have a Vollo image loaded on it or if the device does not enumerate correctly. Programming over PCIe is preferred. If the board does not enumerate or there is some other issue with PCIe programming then JTAG programming is the only option.

This requires a USB cable to be connected to the accelerator card and Vivado to be installed on the system so that the device can be programmed over JTAG.

-

Download and install Vivado Lab Edition:

-

Navigate to the Vivado Design Tools download page.

-

Under "Vivado Lab Solutions" find "Vivado 2025.2: Lab Edition - Linux (TAR/GZIP - 1.99 GB)" (later versions may be available).

-

Download the file and extract it to a directory of your choice. You will need an AMD account to download the file. You can create an account for free.

-

Pick a location to install

Vivado_Lab, e.g./opt/Xilinx, a user directory like~/Xilinxis also fine:VIVADO_DIR=~/Xilinx mkdir -p $VIVADO_DIR -

Extract the tarball:

tar xf Vivado_Lab_Lin_2025.2_1114_2157.tar cd Vivado_Lab_Lin_2025.2_1114_2157 -

Run the installer:

./xsetup --agree 3rdPartyEULA,XilinxEULA --batch Install --edition "Vivado Lab Edition (Standalone)" --location $VIVADO_DIR -

Check that installation was successful:

$ $VIVADO_DIR/2025.2/Vivado_Lab//bin/vivado_lab -version Vivado Lab Edition v2025.2 (64-bit) SW Build 6299465 on Fri Nov 14 21:19:43 MST 2025 Tool Version Limit: 2025.11 Copyright 1986-2022 Xilinx, Inc. All Rights Reserved. Copyright 2022-2025 Advanced Micro Devices, Inc. All Rights Reserved.

-

-

Run the

flash_vollo-silicom-artena-c8b32.tclscript to program the Artena board:sudo $VIVADO_DIR/2025.2/Vivado_Lab/bin/vivado_lab -mode batch -source ./flash_vollo-silicom-artena-c8b32.tclThis prints out a lot of lines while programming and takes about 10 minutes.

If you get an error like this:

ERROR: [Labtoolstcl 44-469] There is no current hw_target.Make sure that you ran

vivado_labwithsudoand that the USB cable is plugged in.After programming you must power cycle the host for the new bitstream to be loaded.

-

If successful the device should now enumerate as a Myrtle.ai Vollo device:

$ lspci -d 1ed9: 01:00.0 Processing accelerators: Myrtle.ai Device 000a 01:00.1 Processing accelerators: Myrtle.ai Device 100a

Programming the FPGA over PCIe

If your FPGA is already programmed with the Vollo accelerator then you can update the bitstream over PCIe. You can check if the device is programmed with the Myrtle.ai Vollo bitstream by running:

$ lspci -d 1ed9:

01:00.0 Processing accelerators: Myrtle.ai Device 000a

01:00.1 Processing accelerators: Myrtle.ai Device 100a

If the device has not been programmed with the vollo bitstream then you will need to program the board over JTAG. See Programming the FPGA via JTAG.

The following instructions will program the Vollo bitstream over PCIe:

-

First load the kernel driver.

sudo ./load-kernel-driver.sh vfio -

Once the kernel driver is loaded you can program the flash with

vollo-tool:sudo $VOLLO_SDK/bin/vollo-tool fpga-config overwrite-partition ${device_index:?} $VOLLO_SDK/bitstream/vollo-silicom-artena-c8b32.pdi USER_IMAGEThe progress will be displayed and it should take a couple of minutes to program the flash. You will need to power cycle the host for the new bitstream to be loaded.

-

If successful the device should now enumerate as a Myrtle.ai Vollo device:

$ lspci -d 1ed9: 01:00.0 Processing accelerators: Myrtle.ai Device 000a 01:00.1 Processing accelerators: Myrtle.ai Device 100a

Programming the V80 FPGA

This section assumes that the Vollo SDK is already installed and set up on the machine that you are using. If you haven't done so already, instructions for how to do that may be found at: Vollo SDK Installation

Make sure the VOLLO_SDK environment variable is set by sourcing setup.sh from the Vollo SDK.

source <path-to-VOLLO_SDK>/setup.sh

Download the bitstream for your FPGA

The bitstream is available on the Github Release page alongside the Vollo SDK. For example to

download the bitstream for the AMD V80 board with the c6b32 configuration of Vollo:

curl -LO https://github.com/MyrtleSoftware/vollo-sdk/releases/download/v27.1.0/vollo-amd-v80-c6b32-27.1.tar.gz

mkdir -p $VOLLO_SDK/bitstream

tar -xzf vollo-amd-v80-c6b32-27.1.tar.gz -C $VOLLO_SDK/bitstream

Alternatively, for the AMD V80LL, use:

curl -LO https://github.com/MyrtleSoftware/vollo-sdk/releases/download/v27.1.0/vollo-amd-v80ll-c6b32-27.1.tar.gz

mkdir -p $VOLLO_SDK/bitstream

tar -xzf vollo-amd-v80ll-c6b32-27.1.tar.gz -C $VOLLO_SDK/bitstream

Programming the FPGA via JTAG

Programming a V80 board over JTAG is necessary if the board does not yet have a Vollo image loaded on it or if the device does not enumerate correctly. Programming over PCIe is preferred. If the board does not enumerate or there is some other issue with PCIe programming then JTAG programming is the only option.

This requires a USB cable to be connected to the accelerator card and Vivado to be installed on the system so that the device can be programmed over JTAG.

-

Download and install Vivado Lab Edition:

-

Navigate to the Vivado Design Tools download page.

-

Under "Vivado Lab Solutions" find "Vivado 2025.2: Lab Edition - Linux (TAR/GZIP - 1.99 GB)" (later versions may be available).

-

Download the file and extract it to a directory of your choice. You will need an AMD account to download the file. You can create an account for free.

-

Pick a location to install

Vivado_Lab, e.g./opt/Xilinx, a user directory like~/Xilinxis also fine:VIVADO_DIR=~/Xilinx mkdir -p $VIVADO_DIR -

Extract the tarball:

tar xf Vivado_Lab_Lin_2025.2_1114_2157.tar cd Vivado_Lab_Lin_2025.2_1114_2157 -

Run the installer:

./xsetup --agree 3rdPartyEULA,XilinxEULA --batch Install --edition "Vivado Lab Edition (Standalone)" --location $VIVADO_DIR -

Check that installation was successful:

$ $VIVADO_DIR/2025.2/Vivado_Lab//bin/vivado_lab -version Vivado Lab Edition v2025.2 (64-bit) SW Build 6299465 on Fri Nov 14 21:19:43 MST 2025 Tool Version Limit: 2025.11 Copyright 1986-2022 Xilinx, Inc. All Rights Reserved. Copyright 2022-2025 Advanced Micro Devices, Inc. All Rights Reserved.

-

-

Run the

flash_vollo-amd-v80-c6b32.tclscript to program the V80 board:sudo $VIVADO_DIR/2025.2/Vivado_Lab/bin/vivado_lab -mode batch -source ./flash_vollo-amd-v80-c6b32.tclThis prints out a lot of lines while programming and takes about 10 minutes.

If you get an error like this:

ERROR: [Labtoolstcl 44-469] There is no current hw_target.Make sure that you ran

vivado_labwithsudoand that the USB cable is plugged in.After programming you must power cycle the host for the new bitstream to be loaded.

Sometimes a V80 host machine will hang on boot. You may need to force another power cycle of the host to bring it back. Occasionally a power cycle isn't enough and you may need to turn the power off for several minutes before turning it back on. -

If successful the device should now enumerate as a Myrtle.ai Vollo device:

$ lspci -d 1ed9: 01:00.0 Processing accelerators: Myrtle.ai Device 000a 01:00.1 Processing accelerators: Myrtle.ai Device 100a

Programming the FPGA over PCIe

If your FPGA is already programmed with the Vollo accelerator then you can update the bitstream over PCIe. You can check if the device is programmed with the Myrtle.ai Vollo bitstream by running:

$ lspci -d 1ed9:

01:00.0 Processing accelerators: Myrtle.ai Device 000a

01:00.1 Processing accelerators: Myrtle.ai Device 100a

If the device has not been programmed with the Vollo bitstream then you will need to program the board over JTAG. See Programming the FPGA via JTAG.

Programming over PCIe is the preferred method of programming the board as it is faster than programming over JTAG, and does not require a USB programming cable or for Vivado to be installed.

-

Build and insert the ami driver.

cd ami_kernel_driver make sudo insmod ami.koThere may be compilation issues with your version of Linux. This has been checked with Rocky Linux 8.10 and Ubuntu 22.04. If there is an issue with your system, please contact us.

-

Once the kernel driver is loaded you can program the flash with

vollo-tool(which usesami_tool). If you only have one board,device_indexis0.sudo $VOLLO_SDK/bin/vollo-tool fpga-config overwrite-partition ${device_index:?} $VOLLO_SDK/bitstream/vollo-amd-v80-c6b32.pdi USER_IMAGEThere will be a progress bar and it should take around 5 minutes to program the flash. You will need to power cycle the host for the new bitstream to be loaded.

Sometimes a V80 host machine will hang on boot. You may need to force another power cycle of the host to bring it back. Occasionally a power cycle isn't enough and you may need to turn the power off for several minutes before turning it back on. -

If successful the device should now enumerate as a Myrtle.ai Vollo device:

$ lspci -d 1ed9: 01:00.0 Processing accelerators: Myrtle.ai Device 000a 01:00.1 Processing accelerators: Myrtle.ai Device 100a

Troubleshooting

Some troubleshooting recommendations may be found in Troubleshooting the V80

Troubleshooting the V80 / V80LL card

This section provides suggested solutions to common problems that are faced when working with the V80 or V80LL. Though only the V80 is referenced in the solutions below, they all apply to both the V80 and V80LL cards.

General troubleshooting

Before trying any other solutions, it's always good practice to power down the host machine and then power it back up again. This can solve configuration issues related to PCIe enumeration and can solve many other problems.

Problems programming the V80 over PCIe

The processes below assume that the V80 has already been successfully programmed with a Vollo image at least once,

either via JTAG or PCIe. If you have not yet programmed the card with a Vollo image, please follow the instructions

in Programming the V80 via JTAG.

If you are having trouble while programming the V80 card over PCIe, or if you cannot access sensor data

from the card, then the first step is to ensure that the ami driver is built and loaded correctly.

cd $VOLLO_SDK/ami_kernel_driver

make

sudo insmod ami.ko

If the driver has already been loaded, try unloading and reloading the driver:

cd $VOLLO_SDK/ami_kernel_driver

sudo rmmod ami

sudo insmod ami.ko

Now that the ami driver is correctly loaded, the driver association with the v80 should be visible with an lspci command.

lspci -vvvnn -s $BDF

If you don't know what your card's BDF is, it may be found by running the command below.

lspci | grep "Myrtle"

Running the full lspci command should display the V80 card loaded with a Vollo image as below. The card's BDF here is 01:00.

01:00.0 Processing accelerators [1200]: Myrtle.ai Device [1ed9:000a]

Subsystem: Xilinx Corporation Device [10ee:50b4]

Control: I/O- Mem+ BusMaster- SpecCycle- MemWINV- VGASnoop- ParErr- Stepping- SERR- FastB2B- DisINTx-

Status: Cap+ 66MHz- UDF- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort- >SERR- <PERR- INTx-

IOMMU group: 12

Region 0: Memory at c0000000 (32-bit, non-prefetchable) [size=256M]

Region 2: Memory at d0000000 (32-bit, non-prefetchable) [size=4M]

Region 4: Memory at fce0000000 (64-bit, prefetchable) [size=4M]

Capabilities: <access denied>

01:00.1 Processing accelerators [1200]: Myrtle.ai Device [1ed9:100a]

Subsystem: Xilinx Corporation Device [10ee:50b4]

Control: I/O- Mem+ BusMaster+ SpecCycle- MemWINV- VGASnoop- ParErr- Stepping- SERR- FastB2B- DisINTx-

Status: Cap+ 66MHz- UDF- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort- >SERR- <PERR- INTx-

Latency: 0

IOMMU group: 13

Region 0: Memory at fcd0000000 (64-bit, prefetchable) [size=256M]

Capabilities: <access denied>

Kernel driver in use: ami

The last line shows the ami driver correctly associated with the 1st physical function of the board, 01:00.1.

This provides access to the OSPI programming functions available on the V80 via PCIe and the normal PCIe programming detailed in Programming the V80 over PCIe should be possible. If not, please continue with this guide.

Recovering the V80 from a "bad state"

The V80 card can sometimes enter into a "bad state". This can result in the card not functioning correctly despite following other troubleshooting steps, including powering down and powering up the host machine.

Such a failure might manifest as follows:

If, while running the PCIe programming commands found in step 2 of Programming the FPGA over PCIe, you see a failure that displays as below, then it's possible that the V80 card is in a bad state.

----------------------------------------------

Device | 01:00.1

----------------------------------------------

Current Configuration

----------------------------------------------

UUID | 611196598b26d6e6896b650e6357e1ba

----------------------------------------------

Incoming Configuration

----------------------------------------------

UUID | 611196598b26d6e6896b650e6357e1ba

Path | /home/stuart/Projects/defaultBuilds/v80ll-sensors-amc-update/pdi/amd_v80_gen5x8_nofpt.pdi

Partition | 0

----------------------------------------------

Are you sure you wish to proceed? [Y/n]: Y

[....................................................................................................] 0% | Error: could not program image

EIO: File could not be read or written [do_image_download:154 - errno 19 (No such device)].

The suggested solution for stateful failures like this is to:

- Power the host machine down

- Completely remove power from the host machine by either unplugging or removing the card from the host machine completely.

- Leave the host machine and/or V80 card unpowered for around 30 minutes.

- Reinsert the V80 into the host machine (if removed), reconnect power to the host machine.

- Power up the host machine again.

- Re-attempt PCIe programming following the steps provided in Programming the FPGA over PCIe.

This unorthodox solution has been found to work in many cases and is indeed the recommended solution to these problems as provided by AMD in their support forum.

Licensing

Vollo is licensed on a per-device basis.

Redeeming licenses with vollo-tool

You will receive a purchase-token with your Vollo purchase. The purchase-token can be used to redeem Vollo licenses for a set number of devices.

To see the number of credits (i.e. the number of devices which can be redeemed) on your purchase-token, run:

source setup.sh

vollo-tool license num-remaining-devices -t <purchase-token>

To redeem devices on your purchase token:

-