Programming the Agilex FPGA

This section assumes that the Vollo SDK is already installed and setup on the machine that you are using. If you haven't done so already, instructions for how to do that may be found at: Vollo SDK Installation.

Make sure the VOLLO_SDK environment variable is set by sourcing setup.sh from the Vollo SDK.

source <path-to-VOLLO_SDK>/setup.sh

Download the bitstream for your FPGA

The bitstream is available on the Github Release page alongside the Vollo SDK.

For example to download the bitstream for the Agilex ia840f board with the c2b64d configuration of Vollo:

curl -LO https://github.com/MyrtleSoftware/vollo-sdk/releases/download/v27.0.1/vollo-ia840f-c2b64d-27.0.tar.gz

mkdir -p $VOLLO_SDK/bitstream

tar -xzf vollo-ia840f-c2b64d-27.0.tar.gz -C $VOLLO_SDK/bitstream

The Agilex-based boards that are currently supported are:

-

Bittware IA420F

-

Bittware IA840F

-

Napatech NT400D11 (Link programmable version)

Note on programming the Napatech NT400D11 over JTAG

The NT400D11 card needs additional cabling beyond a USB cable to program the board over JTAG. This cabling is provided as a development kit by Napatech (PGM-DEVKIT-IFPGA-DF52-2XIDC-UART, product number: 802-0116-01-10) and includes:

-

An Intel® FPGA USB-Blaster II cable and,

-

A Napatech Passive FPGA Download Cable converter box

These two cables must be connected to each other as shown in the image below:

To connect this cable array to the Napatech board, the long thin plug should be connected to the connector shown in the following image:

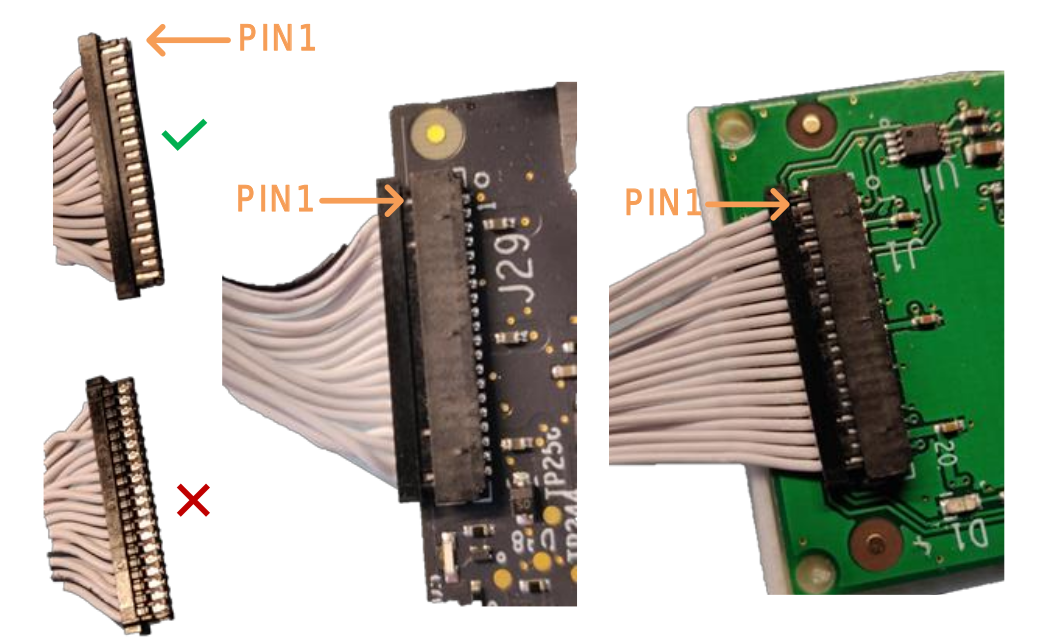

In order to correctly couple these two connectors, observe the conventions shown in the following image:

Connector the USB side of the cable array to a high-speed USB port on your host PC and the follow the rest of the directions in the next section.

Programming the FPGA via JTAG

If your FPGA is not already programmed with the Vollo accelerator then please follow these instructions to load the bitstream into the accelerator card's flash memory.

This requires a USB cable to be connected to the accelerator card and Quartus programmer to be installed on the system so that the device can be programmed over JTAG.

If the FPGA card already has a Vollo Accelerator Bitstream, it can be updated over PCIe by following the steps in the section Program the FPGA via PCIe below. Note that you only need to update the bitstream if updating to an incompatible version of the Vollo SDK. Programming over PCIe is faster than programming over JTAG, and does not require a USB programming cable or for Quartus Programmer to be installed.

-

Download and install the latest Quartus Programmer:

- Navigate to https://www.intel.com/content/www/us/en/software-kit/782411/intel-quartus-prime-pro-edition-design-software-version-23-2-for-linux.html.

- Select

Additional Softwareand scroll down to find the Programmer. - Follow the instructions for installation.

-

Add Quartus programmer to your path:

export QUARTUS_DIR=<path to qprogrammer install> export PATH=$QUARTUS_DIR/qprogrammer/quartus/bin:$PATH -

Start the jtag daemon:

sudo killall jtagd sudo jtagd -

Run

jtagconfigfrom the Quartus install, you should see the device(s):$ jtagconfig 1) IA-840F [1-5.2] 0341B0DD AGFB027R25A(.|R0)or, for the NT400D11:

$ jtagconfig 1) USB-BlasterII [1-5] C34320DD AGFA014R24C(.|B|AA) -

Navigate to the directory containing the

jicfile:cd $VOLLO_SDK/bitstream -

Set the JTAG clock frequency of the device you want to program to 16 MHz. Specify the device by providing the name returned by

jtagconfig:jtagconfig --setparam "IA-840F [1-5.2]" JtagClock 16Mor, for the NT400D11:

jtagconfig --setparam "USB-BlasterII [1-5]" JtagClock 16M -

Start the programming operation on the chosen device. This takes around 20 minutes. For the IA840F:

quartus_pgm -c "IA-840F [1-5.2]" -m JTAG -o "ipv;vollo-ia840f-c3b64.jic"or, for the IA420F:

quartus_pgm -c "IA-420F [1-5.2]" -m JTAG -o "ipv;vollo-ia420f-c6b32.jic"or, for the NT400D11:

quartus_pgm -c "USB-BlasterII [1-5]" -m JTAG -o "ipv;vollo-nt400d1-c6b32.jic" -

Go back to 6 and program any other devices.

-

Power off the system and start it back up. The bitstream will now be loaded onto the FPGA.

For the configuration process to be triggered the board has to register the power being off. It is recommended to turn the power off and then wait a few seconds before turning the power back on to ensure this happens. -

Check a Vollo bitstream is loaded:

$ lspci -d 1ed9:766f 51:00.0 Processing accelerators: Myrtle.ai Device 766f (rev 01)Check the correct Vollo bitstream is loaded:

vollo-tool bitstream-check bitstream/<bitstream-name>.json

Programming the FPGA via PCIe

NOTE: this can only be done with an FPGA that is already programmed with a Vollo bitstream.

-

Load the kernel driver:

sudo ./load-kernel-driver.sh -

Check the current bitstream information:

source setup.sh vollo-tool bitstream-info -

Check that the device is set up for remote system updates by running the command below, with

device indexrepresenting the index of the device you want to update, in the order shown in the previous command, starting from 0. It should print ajsonstring to the terminal showing the device status.vollo-tool fpga-config rsu-status <device index> -

Update the

USER_IMAGEpartition of the flash with the new bitstream image contained in therpdarchive in the$VOLLO_SDK/bitstreamdirectory. This should take around 5 minutes. Do not interrupt this process until it completes.sudo ./load-kernel-driver.sh vollo-tool fpga-config overwrite-partition <device index> <.rpd.tar.gz file> USER_IMAGE -

Repeat step 4 for any other devices you wish to update.

-

Power off the system and start it back up.

For the configuration process to be triggered the board has to register the power being off. It is recommended to turn the power off and then wait a few seconds before turning the power back on to ensure this happens. -

Repeat steps 1, 2 and 3. The

bitstream-infocommand should show that the updated bitstream has been loaded (e.g. a newer release date), and the output of thersu-statuscommand should show all zeroes for theerror_codeandfailing_image_addressfields. -

Check the correct Vollo bitstream is loaded:

sudo ./load-kernel-driver.sh vollo-tool bitstream-check bitstream/<bitstream-name>.json